# SPE for automotive and the transfer into industrial automation

By Dr. Michael Wollitzer

Rosenberger Hochfrequenztechnik

#### SPE for automotive and the transfer into industrial automation

#### Rosenberger

One of the worldwide leading manufacturers of standard and customer specific connectivity solutions.

Dr. Michael Wollitzer Head of R&D at Rosenberger

В

- Ethernet/IP-Networking is agnostic to PHY-layer

- Motivation for Single Pair Ethernet

Lessons learned in Automotive Applications

D

Power over Datalines (PoDL) reduces Harness Complexity

# Ethernet/IP-Networking is agnostic to PHY-layer A

00

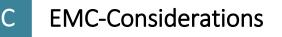

## Ethernet and the OSI-Layer-Model

#### Application Layers do not care about physical Implementation

| OSI-Layer            | "Ethernet"                                           |              |                     |

|----------------------|------------------------------------------------------|--------------|---------------------|

| 7 Application Layer  | Application Layer                                    |              |                     |

| 6 Presentation Layer | (DNS, FTP, HTTP, NNTP, SMTP, SNMP, SSH,<br>TELNET, ) |              |                     |

| 5 Session Layer      |                                                      |              |                     |

| 4 Transport Layer    | Transport-Layer (TCP/IP)                             |              |                     |

| 3 Network Layer      | Internet Laver (TCD/ID)                              | Media        |                     |

| 2 Data Link Layer    | Logical Link Control (LLC), IEEE 802.2               | Independent  |                     |

|                      | Media Access Control (MAC), IEEE 802.1 5             | Interface,   |                     |

| 1 Physical Layer     | Reconciliation, IEEE 802.3                           | MII, GMII, … |                     |

|                      | Physical Coding Sublayer (PCS)                       | Media        | Y                   |

|                      | Physical Medium Dependent (PMD)                      | Dependent    |                     |

|                      |                                                      | Interface,   |                     |

|                      |                                                      |              |                     |

|                      | Medium                                               | CAT-Cable,   | Single Pair Etherne |

|                      |                                                      | SPE, Optics, | System Alliance     |

### Ethernet and the OSI-Layer-Model

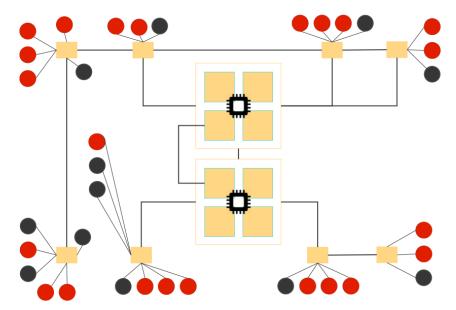

#### Trends in architecture

- Zone architecture

- Redundancy for autonomous driving

- Asymmetrical date rates

**Traditional architecture**

Domain architecture

Asymmetric Data Requirement

## B Motivation for Single Pair Ethernet

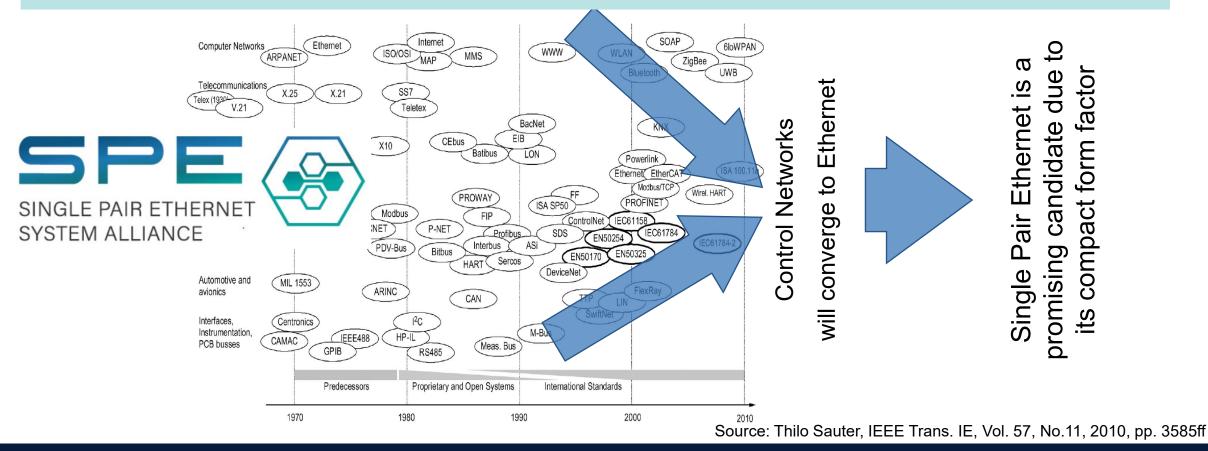

#### Convergence to Single Pair Ethernet

#### The wild zoo of Standards for Networking of Devices will Converge to (Single Pair) Ethernet

00

## Motivation for Single Pair Ethernet

#### Why Single Pair Ethernet?

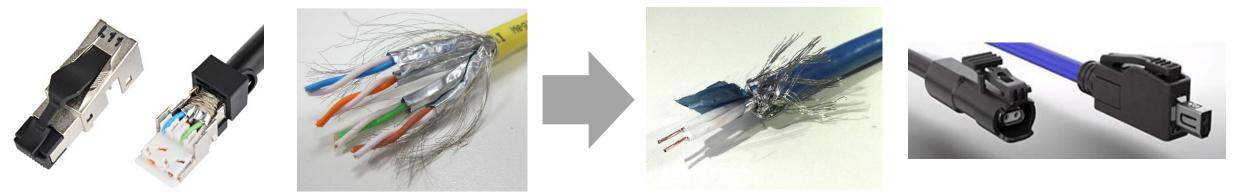

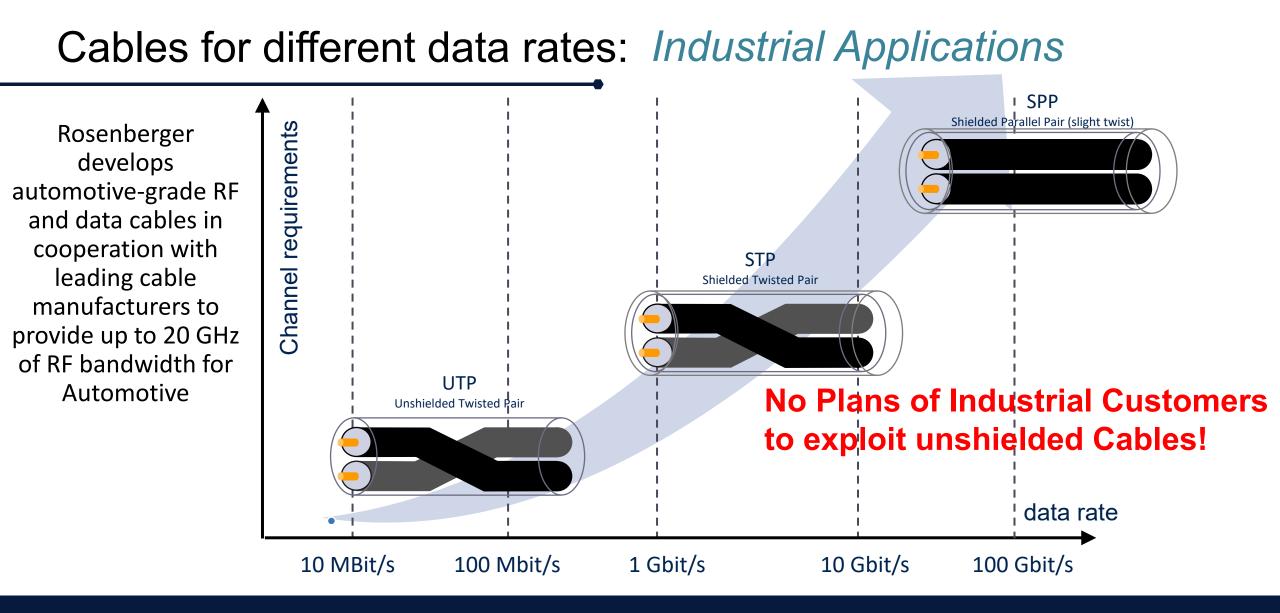

- Current physical layer implementation: eight wire (four pair) CAT-cables

- Connectivity via RJ45 (eight terminals plus shield)

- Has drawbacks concerning complexity, weight, space consumption, field confectioning, physical flexibility, connector reliability, signal reliability

- Single Pair Ethernet is a means to improve electrical and mechanical properties of the PHY-layer (reliability, signalling performance, assembly automation ...)

## Motivation for Single Pair Ethernet

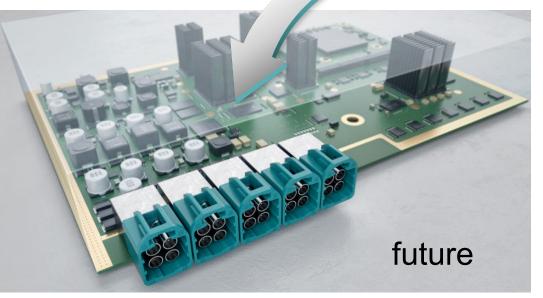

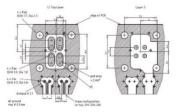

#### Miniaturization

- Miniaturization of the connector's footprint on interconnect panels is desired in future applications

- Miniaturization leads to limitations on the physical dimensions of the cables

- Connectors get smaller but cables should be larger for low attenuation -> Compromise to be found

Cables should target diameter < 5 mm for differential links</li>

## Finalized IEEE-Standards for SPE

| IEEE-Standard                                                | Technical Comment                                                                                                                                                                                                                          |

|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IEEE P802.3cg<br>(10Base-T1); still in Draft Version         | 10 Mbit/s SPE, PAM-3?,<br>2.4V-Operation has 1000 m Reach,<br>1.0V-Operation has 15 m Reach                                                                                                                                                |

| IEEE 802.3bw-2015<br>(100Base-T1); finalized                 | 100 Mbit/s SPE, PAM-3, 4B/3B-coding<br>Spec for reach up to 15 m is finalized; longer links to be specified<br>in future releases; no physical reason, why<br>100 m-links should not work (consider propdelay-spec!)                       |

| IEEE 802.3bp-2016<br>(1000Base-T1); finalized                | 1000 Mbit/s SPE, PAM-3, 80B/81B-coding<br>Spec is finalized; link segments<br>type A (15 m, propagation delay < 94 ns) and<br>type B (40 m, propagation delay < 234 ns) are specified<br>100 m-links not feasible with current technology; |

| IEEE 802.3bu-2016<br>(PoDL; Power over DataLines); finalized | Power over DataLines specified for 100Mbit/s- and 1000Mbit/s-<br>Operation; Loop Resistance has to be very low depending on<br>power class; power at device up to 50 W<br>Additional ferrite components req'd                              |

## Estimation of Req'd Wire CrossSection

| SPE-Datarate as specified in IEEE                     | Length | Spec'd Frequency<br>max. spec'd IL                                                        | Conductor CrossSection /<br>sqmm @ Tamb = 85°C | AWG |  |

|-------------------------------------------------------|--------|-------------------------------------------------------------------------------------------|------------------------------------------------|-----|--|

| 10 Mbit/s                                             | 1000 m | 20 MHz, 58.35 dB                                                                          | 0.792                                          | 18  |  |

| 10 Mbit/s                                             | 500 m  | 20 MHz, 58.35 dB                                                                          | 0.201                                          | 24  |  |

| 10 Mbit/s                                             | 100 m  | 20 MHz, 58.35 dB                                                                          | 0.0089                                         | 37  |  |

| 100 Mbit/s                                            | 15 m   | 66 MHz, 7.2 dB                                                                            | 0.0425                                         | 30  |  |

| 1000 Mbit/s                                           | 15 m   | 600 MHz, 15.88 dB                                                                         | 0.0904                                         | 27  |  |

| 1000 Mbit/s                                           | 40 m   | 600 MHz, 22.27 dB                                                                         | 0.292                                          | 22  |  |

| 1000 Mbit/s<br>(not spec'd! Just for<br>comparison!!) | 100 m  | 600 MHz, 22.27 dB<br>(40 m loss budget assumed.<br>Propagation delay will not meet spec!) | 1.69                                           | 14  |  |

Assumptions: Validity of scaling models; dielectric losses negligible

## Why EMC takes a Major Role in the car

- EMC means: "the ability of equipment or a system to function satisfactorily in its electromagnetic environment without introducing intolerable electromagnetic disturbances to anything in that environment."

- "The aim of EMC is to ensure the reliability and safety of all types of systems wherever they are used and exposed to electromagnetic environments. So EMC development is closely linked with the whole field of electrical and electronic engineering, including the design and testing of these systems."

$\ldots$  found on the IEC Homepage

Si Sy

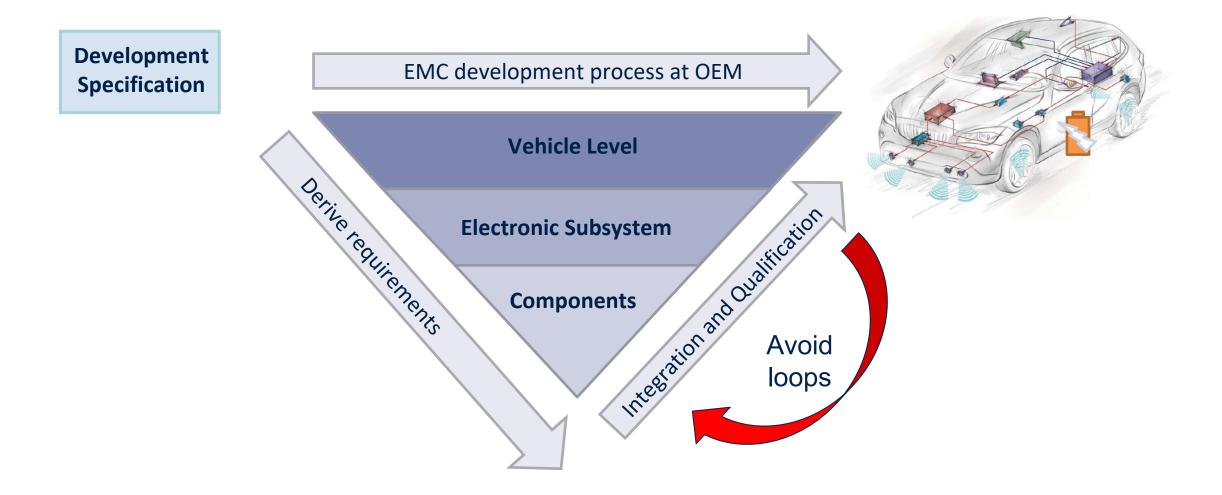

## The V-Model in EMC-robust Design

### Automotive Ethernet Status of Implementation

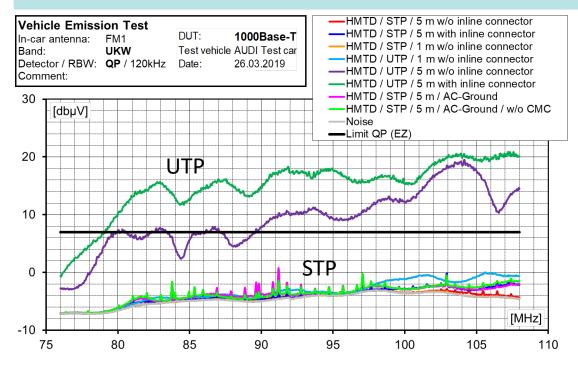

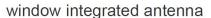

### 1000BASE-T1 Vehicle Measurement

#### **Measurement results**

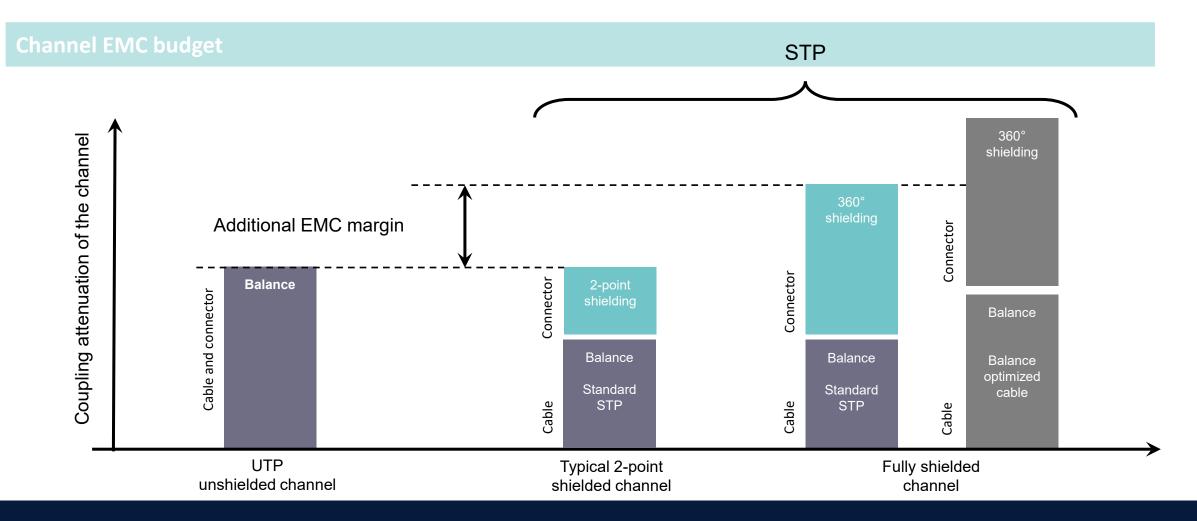

- H-MTD with UTP: 1 m link passes, 5 m link above the limit for emissions into antenna

- H-MTD with STP passes with margin (noise level)

- To implement UTP for 1000BASE-T1, the OEM should test EMC on vehicle level

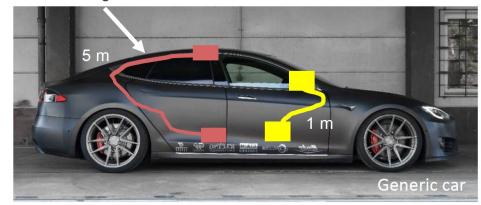

#### **Crosstalk in Bundles**

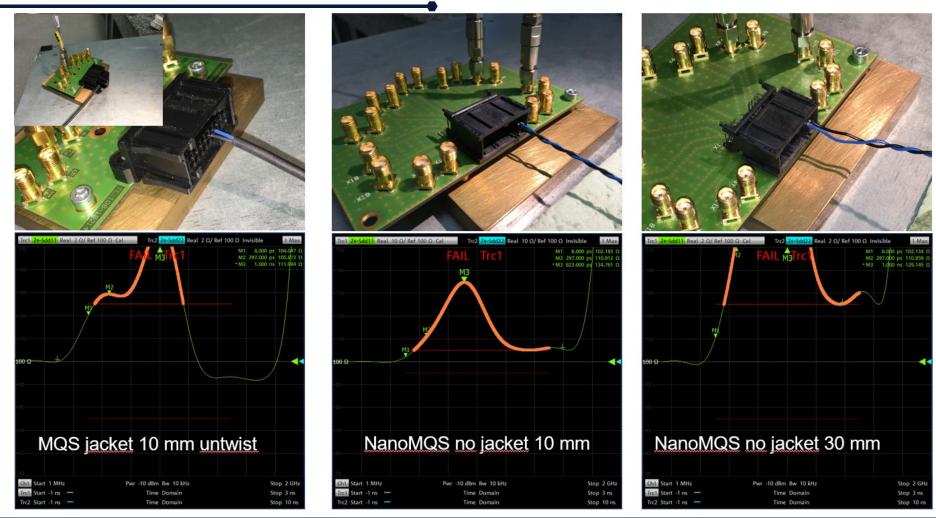

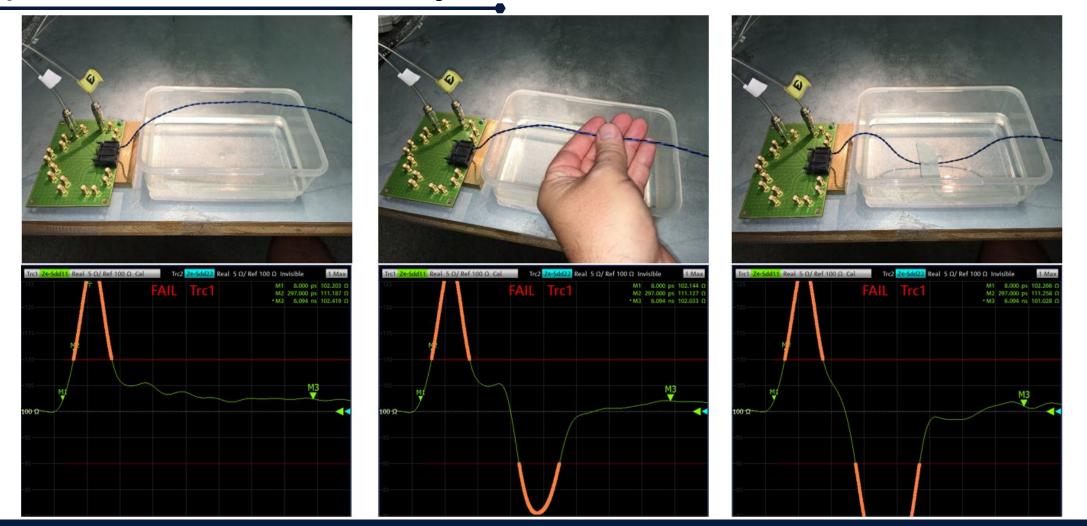

## D Lessions learned in Automotive Applications

#### Untwist

#### Exposure to water – Non-jacketed UTP

### Automotive Ethernet

#### **Design-In Support**

- Contribute in standardization

- Collaborate with PHY vendors

- Layout recommendations

- Signal path layout review

- EMC aspects of PCB grounding concepts

- Test adapters and break-out boards

- Measurement couplers for debugging in the car

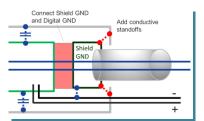

# E Power over Datalines (PoDL) reduces Harness Complexity

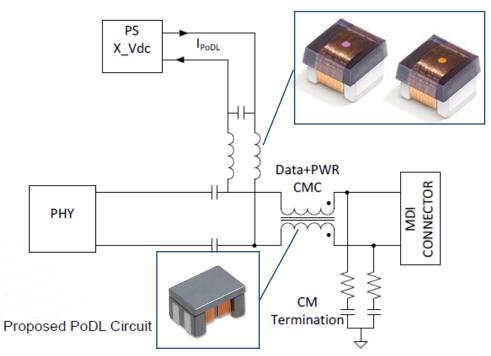

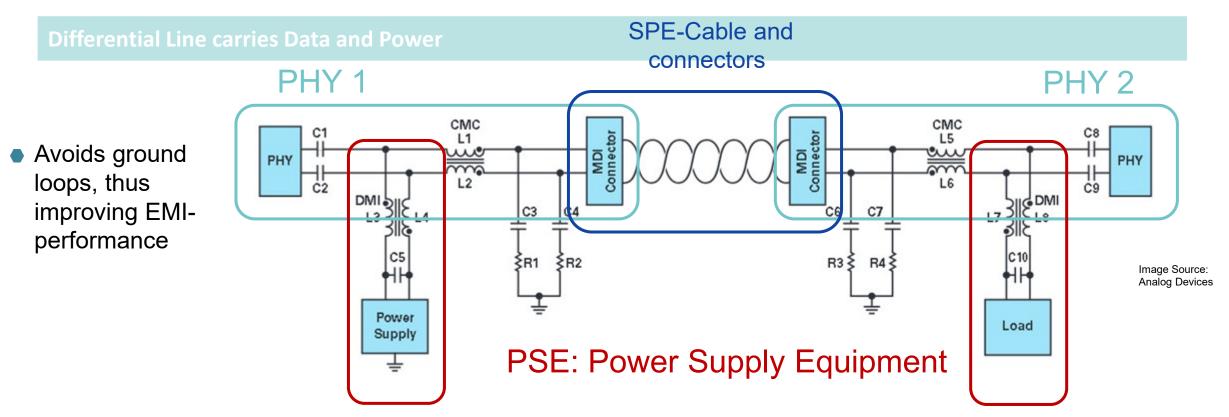

## Power over Dataline (PoDL)

- Specified for SPE in IEEE 802.3bu

- Transmission of DC-power on a signal pair on top of the datastream is more difficult than if shield is used as DC-return (forward- reverse current act like a differential signal)

- Current rating is limited by the inductor's properties

- RF-properties (physical size of the ferrite components!)

- Symmetry

- Wire dimensions

- Ferrite core material (saturation effects!)

- DC resistance of the signal wires and thus voltage drop on the cable limit the possible cable length

## Power over DataLines (PoDL); IEEE 802.3bu-2016

Transmission of data and energy on one cable;

no additional power cable is required! No inductive coupling loops!

## Power over DataLines (PoDL)

| System Class                          |      |       |       |       |       |       |       |       |        |

|---------------------------------------|------|-------|-------|-------|-------|-------|-------|-------|--------|

| $R_{Loop}$ loss                       | I    | I     | II    | Ш     | III   | III   | IV    | V     | VI     |

| 20%                                   | (5V) | (12V) | (12V) | (24V) | (24V) | (48V) | (48V) | (48V) | (Open) |

| *V <sub>PSE(max)</sub> (V)            | 5.5  | 14    | 14    | 28    | 28    | 56    | 56    | 56    | -      |

| *V <sub>PSE(min)</sub> (V)            | 4.75 | 9     | 9     | 18    | 18    | 36    | 36    | 36    | -      |

| I <sub>PI(max)</sub> (A)              | 0.53 | 0.28  | 0.69  | 0.35  | 0.69  | 0.35  | 0.87  | 2.08  | -      |

| ** $R_{Loop(max)}\left(\Omega\right)$ | 1.8  | 6.5   | 2.6   | 10.4  | 5.2   | 20.7  | 8.3   | 3.5   | -      |

| ***P <sub>PD(max)</sub> (W)           | 2    | 2     | 5     | 5     | 10    | 10    | 25    | 60    | -      |

| P <sub>PSE</sub> (W)                  | 2.5  | 2.5   | 6.25  | 6.25  | 12.5  | 12.5  | 31.25 | 75    | -      |

| V <sub>PD(min)</sub>                  | 3.8  | 7.2   | 7.2   | 14.4  | 14.4  | 28.8  | 28.8  | 28.8  | -      |

$^*V_{\mathsf{PSE}}$  is the open circuit voltage measured at the PSE PI.  $^{**}\mathsf{R}_{\mathsf{Loop}}$  is defined as the sum of the PSE source resistance and link segment round trip resistance.

\*\*\*P<sub>PD</sub> is measured at the PD PI.

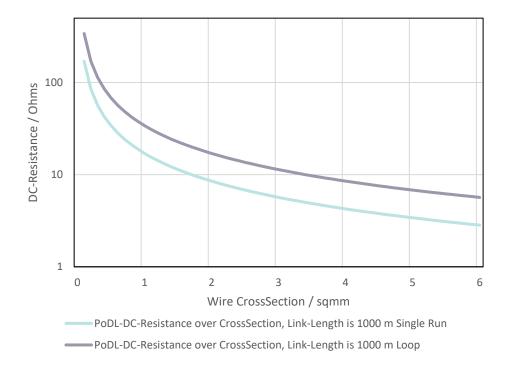

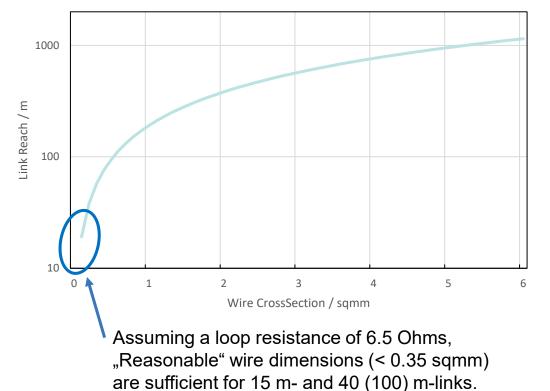

### Power over DataLines (PoDL): 10Base-T1 over 1000 m

#### Reach according to IEEE-Specs at Room Temperature; Assessment based on Loop Resistance

Link Resistance over Wire-CrossSection

Cable dimensions get unrealistically large for 1000 m-links!

Link Reach over Wire-CrossSection

# Thank You

#### Contact details

#### Rosenberger

#### **Keller Thomas**

**Business Area Medical & Industries**

Product Manager

Phone: +49 8684 18-1952

Cell: +49 151 18609451

E-mail: <u>thomas.keller@rosenberger.com</u>

Rosenberger Hochfrequenztechnik GmbH & Co. KG Hauptstraße 1, 83413 Fridolfing, Germany

www.rosenberger.com